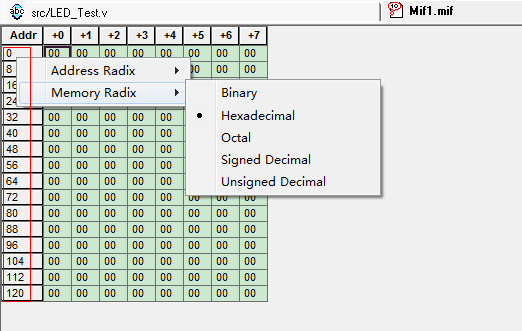

In the text editor, add the following line to the end of file: alias mars='java -jar /usr/local/3rdparty/csce611/mars/mars.jar' Save the file and close the editor. We have installed MARS in a shared directory, but in order to avoid the need to specify its entire path, you can specify a UNIX alias to make it more convenient to run MARS. MARS is an improved version of the SPIM simulator that you may have used in CSCE 212. For this, we will use a Java-based MIPS simulator called MARS. You can copy the generated code and include it in your project if you want, but it's the best way to get what you want.1 Generating MIF files Introduction In order to load our handwritten (or compiler generated) MIPS assembly problems into our instruction ROM, we need a way to assemble them into machine language and then save these machine language programs in a text file where the binary machine instructions are represented as a sequence of ASCII hexadecimal values.

You want to find the correct doc for your version of quartus. This is Intel's doc that shows you how to infer BRAMs: but it's for Quartus Pro. This page provides some VHDL templates to infer a BRAM. Here is the doc you need that describes them: In the MAX10 (yoru FPGA for what I can tell) the BRAMs are called M9Ks. AKA instantiate an intel provided IP core.Ģ) Write RTL in a very specific way that the tools can use to infer a BRAM. (depending on which quartus version you use). Use the IP catalogue / megawizzard / platform designer / qsys. Now to instantiate a BRAM you have two approaches. But note that "memory bits" is 0 in both of your reports. The difference in number of logic elements / registers is probably down to how you access the data. In both of your examples, you are using distributed RAM. As a rule of thumb, if you want to store more than say ~256 bytes you probably want to use a BRAM. That said, they are fast, and dense storage. They are also of fixed sizes, so if you only want to store 4 bytes, there's not much point. So a read may have 1, 2 or even 3 cycles of latency on it. In general you can only access 1 (single port) or 2 (dual port) entries at once, and you may be required to have registers on inputs and / or outputs. This is a special hardware RAM.įor distributed logic you can do stuff like: may_ram <= foo ĪKA you can access as many locations as you want on every clock tick.Ī BRAM being a specific hardware block is more constrained. This is using registers / LUTs spread across the FPGA.Ģ) Using a BRAM.

0 kommentar(er)

0 kommentar(er)